eSi-RISC处理器IP

可配置嵌入式RISC处理器IP

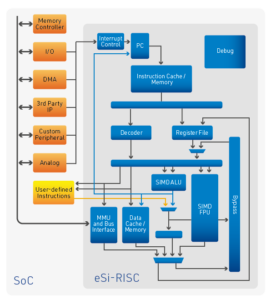

eSi-RISC是面向嵌入式市场的深度可定制处理器架构,可满足嵌入式市场各类应用场景。

从0.35微米到16纳米FinFET,eSi-RISC IP核经过了大量的ASIC和FPGA设计验证。

- 可配置为16位或32位,5级流水线,load-store架构;

- 最小的16位配置只需要耗用8000个ASIC门单元。

- 支持16位和32位指令混合,极大的提升代码密度,缩减代码大小。

- 采用业界标准的核间互联总线协议(AMBA AXI/AHB/APB)。

- 可选配多核,SIMD引擎以及浮点处理单元。

- 通过IP的裁剪加上定制指令,eSi-RISC可以达到极低的功耗。

- 支持用户态和特权态两种模式。支持硬件嵌套中断。

- 支持通过JTAG或串口调试硬件,还支持附加的硬件跟踪功能。

- 最多可以达到4.12 CoreMark/MHz。