eSi-RISC Processor IP

Configurable Embedded RISC Processor IP

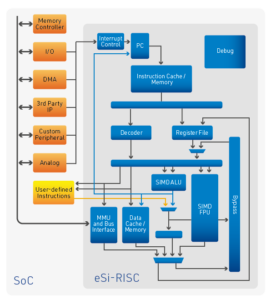

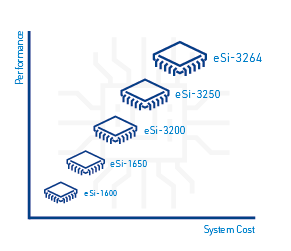

eSi-RISC is a highly configurable microprocessor architecture for embedded systems, that scales across a wide range of applications.

The eSi-RISC IP core has been silicon proven in a wide range of ASIC and FPGA technologies, from 0.35um to 16nm FinFET.

- Configurable 16 or 32-bit, 5-stage pipelined RISC, load-store architecture.

- Implemented in as little as 8k ASIC gates for minimum 16-bit configuration.

- Intermixed 16 and 32-bit instructions gives exceptional code density.

- Uses industry standard bus architecture for IP interconnection (AMBA AXI/AHB/APB).

- Multiprocessor, SIMD and floating-point options.

- Configurability and custom instructions will deliver a solution with exceptionally low-power.

- Supports user and supervisor modes and HW nested interrupts.

- JTAG or serial hardware debug, with optional trace.

- Up to 4.12 CoreMark per MHz.

![]()

Document Downloads