eSi-3200

32 bit Processor, Low-Cost & Low-Power CPU

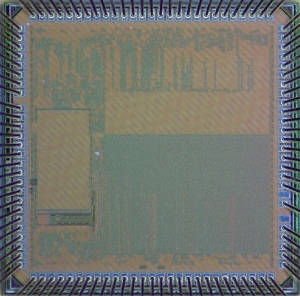

Our eSi-3200 32-bit processor CPU IP core is an extremely small, low-cost and low-power processor ideal for integration into ASIC and/or FPGA designs with on-chip memories. The eSi-3200 is particularly suited to embedded control applications.

Download Documents

32-bit Processor: eSi-3200 Technical Overview

Features

- 32-bit RISC architecture

- 16 or 32 general purpose registers

- 104 basic instructions and 10 addressing modes

- Optional IEEE 754 floating point unit (FPU)

- Supports up to 74 user-defined instructions

- 5-stage pipeline

- Optional memory protection unit (MPU)

- AMBA AXI or AHB interconnect and APB peripheral bus

- Optional support for user and supervisor modes

- Up to 32 vectored interrupts plus NMI and system call

- HW nested and prioritizable interrupts

- Fast interrupt response time of 6-9 cycles

- JTAG or serial debug, with optional trace and performance counters

- Up to 4.12 CoreMark per MHz

- Multiprocessor support

- Intermixed 16 and 32-bit instructions result in exceptional code density without compromising performance

- ASIC performance (Typical 28nm):

- Up to 1 GHz

- From 15k gates

- From 4uW/MHz

- High quality IP:

- Verilog RTL

- DFT ready

- Silicon proven

- C and C++ software development using license-free toolchain, under industry standard Eclipse IDE

- Easy migration path to 16-bit version or 32-bit version with caches

Architecture

The eSi-3200 32-bit CPU is the mid-range member in the eSi-RISC family of processor cores. It is targeted specifically for low-power applications that require more computational power or a larger address space than is provided by the 16-bit eSi-1600 and that are able to be implemented using on-chip memory.

The cacheless memory architecture of the eSi-3200 allows for deterministic performance, making it particularly suitable for hard real-time control applications. It uses a modified-Harvard memory architecture allowing for simultaneous instruction and data fetch. The 5-stage pipeline allows GHz clock frequencies to be achieved.

The eSi-3200’s instruction set includes everything you would expect in a high-performance processor. There are a number of optional application specific instructions and addressing modes. A set of IEEE-754 compliant single-precision floating point instructions are available. Integer arithmetic instructions include a full 64 multiply and accumulate and divide. Bit manipulation instructions such as bitfield extract and insert, count leading zeros, population count, find first set and bit reverse can be included. Integer square root, absolute value, min/max, CRC and parity are also available. 32-bit SIMD instructions with 16-bit elements exploit data parallelism and reduce loop counts. Wait-for-interrupt instructions allow fast entry to low power states, enabling clock and power gating.

For those applications that require extreme performance or ultra low power operation, user-defined instructions and registers can be implemented. Instructions are encoded in either 16 or 32-bits, with all of the commonly used instructions being encoded in 16-bits, maximizing code density and minimizing instruction fetch power consumption.

The processor supports both user and supervisor operating modes, with privileged instructions and memory areas via the optional MPU, to allow an O/S kernel to be fully protected from user applications.

Hardware debug facilities include hardware breakpoints, watchpoints, trace, null pointer detection and single stepping for fast debugging of ROM, FLASH and RAM based programs.

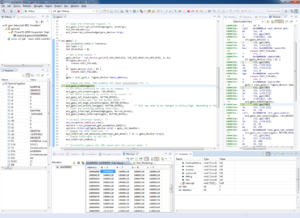

Toolchain

The toolchain is based upon the industry standard GNU toolchain, which includes an optimising C and C++ compiler, assembler, linker, debugger, simulator and binary utilities. All these tools can be driven by the customisable Eclipse IDE or from the command line.

The debugger can connect to HW targets via a low cost USB-JTAG adaptor and RTL simulation via a Verilog PLI library.

Complete C & C++ libraries are supplied. Ports of Micrium’s uC/OS-II RTOS, ThreadX, FreeRTOS and the lwIP TCP/IP stack are available. The toolchain is available for both Windows and Linux hosts and is available to use at no additional cost.

IP Delivery

The eSi-3200 is delivered as a Verilog RTL IP core. The design is target technology independent and DFT ready, supporting full scan insertion for all flip flops and memory BIST. Example scripts are also provided.

A selection of AMBA peripherals can be supplied with the core, including: UART, SPI, I2C™, I2S, Timer, PWM, Watchdog, GPIO, PS/2, RTC, Ethernet MAC, USB, FIFO, Scatter-Gather DMA, AES, SHA, ECC and a quad-SPI Flash interface. By using an industry standard bus, a wide range of 3rd party IP cores are compatible with the eSi-3200.

eSi-RISC can generate a multilayer AHB matrix and APB bus to connect the eSi-3200 CPU, memory and peripherals, according to a customer’s specification.