eSi-Floating Point

The eSi-Floating Point IP cores perform half-precision (16-bit), single-precision (32-bit) and double-precision (64-bit) floating-point arithmetic according to the IEEE 754-2008 standard. The following operations are supported by the floating point IP library:

- Addition and subtraction

- Multiplication

- Division

- Square-root

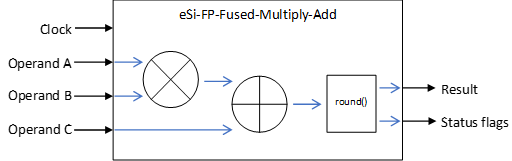

- Fused multiply and add

- Integer to floating-point conversion

- Floating-point to integer conversion

The cores support:

- Rounding to the nearest even number

- Infinities

- NaNs (Not a number) – both quiet and signalling

- Denormalized (subnormal) numbers

- Status flags indicating invalid, divide by zero, overflow, underflow and inexact exceptions

The cores are fully pipelined enabling each core to produce one result per clock cycle. The number of pipeline stages is configurable to trade-off frequency versus latency.

The IP cores are delivered in Verilog HDL. The cores are technology independent and so are suitable for ASIC or FPGA and are DFT ready.