eSi-3200

32位处理器,低成本,低功耗CPU

eSi-3200 32位处理器IP核是一款面积很小,成本和功耗都很低的处理器。其非常适合被整合进带有片上内存的ASIC或FPGA设计。 eSi-3200尤其适合嵌入式控制的应用场景。

下载文档

下载…

eSi-RISC手册

eSi-3200手册

eSi-RISC架构手册 {需要签订NDA}

32位处理器: eSi-3200技术总览

IP特征

- 32位精简指令(RISC)架构

- 16或32个通用寄存器

- 104条基本指令,10种寻址模式

- 可选的IEEE 754浮点运算单元(FPU)

- 最大支持74条用户自定义指令

- 5级流水线

- 可选内存保护单元(MPU)

- AMBA AXI或AHB核间互联总线,APB外设总线

- 可选用户态和特权态支持

- 最大32个中断向量,支持不可屏蔽中断(NMI)和系统调用

- 支持硬件中断嵌套,支持中断优先级

- 6-9个时钟周期的快速中断响应

- 支持JTAG和串口调试,可选硬件跟踪和性能统计计数器

- 最大4.12 CoreMark/MHz

- 支持多核

- 支持混合16位和32位指令,在不牺牲性能的情况下带来最大的代码密度

- ASIC性能(以典型的28纳米制程为例):

- 最大频率高至1GHz

- 最小逻辑门数目低至15000个

- 功耗比低至4uW/MHz

- 高质量的IP:

- 基于Verilog RTL

- 充分考虑测试,满足DFT的标准

- 经过量产检验的质量保证

- 提供免授权费的C/C++程序开发环境,基于业界标准的Eclipse IDE

- 迁移到16位IP或者带缓存的32位IP非常的容易

核心架构

eSi-3200 32位CPU是eSi-RISC IP家族的中端处理器核。 它主要面向低功耗但是又要求一定算力或者较大的地址空间的应用场景。在这些场景下,16位处理器的地址空间通常不够用。这些地址空间可以通过片上内存来实现。

不带缓存的eSi-3200提供完全可预测的性能,这也使得它非常适合被应用到具有高实时性要求的控制场景。 它使用改进过的哈佛结构,同时支持取指令和取数据。 其内部的5级流水线设计能有效的支持高达1GHz的时钟频率。

eSi-3200的指令集基本包含了常见的高性能处理器中的所有指令。 它同时提供一系列的应用场景可选指令和寻址模式。 还支持一系列的IEEE-754单精度浮点指令。 整型算术指令支持64位乘除和累乘。 支持位操作指令,比如位提取,位插入,clz,popcnt,ffs和位翻转等。 支持整数平方根,绝对值,min/max,crc和partiy指令。 支持32位SIMD引擎,操作两路16位数据,有效的提高并行度,减小循环次数。 Wait-for-interrupt指令允许快速的进入低功耗状态,支持对时钟频率和功耗进行限制。

对于那些需要极高的性能或者极低的功耗的场景,可以通过用户自定义指令和寄存器来支持实现。 同时支持16位和32位指令编码,常用的指令都有16位编码,最大程度的提高代码密度,缩小取指功耗。

同时支持用户态和核心态,特权指令和内存保护可以通过可选的MPU实现,操作系统可以跟应用程序有效隔离,从而得到充分的保护。

硬件调试支持硬件断点,观察点,跟踪,性能计数器,空指针探测,单步。这些特性可以有效的支撑对运行在ROM,FLASH和RAM上的程序进行快速调试。

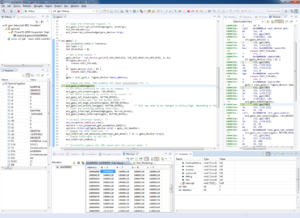

工具链

工具链基于业界标准的GNU工具链,包含C/C++优化编译器,汇编器,链接器,调试器,仿真器和其他二进制工具。 所有的这些工具同时支持集成到Eclipse IDE中,或者作为命令行工具直接调用。

调试器可以通过低成本的USB-JTAG转换器连接到硬件调试对象,也可以通过Verilog PLI库运行RTL仿真。

支持完整的C/C++库。 带eSi-RISC支持的Micrium uC/OS-II RTOS,ThreadX,FreeRTOS。这些RTOS还支持lwIP TCP/IP协议栈。 工具链支持Windows,Linux两种平台。工具链不收取额外的授权费。

IP发布

eSi-3200以Verilog RTL IP核的形式发布。 我们的设计非常的中性,不偏向特别的技术框架。 设计时充分考虑了测试,考虑了DFT,支持在所有的时钟沿插入扫描,还支持内存BIST。 对于常用的EDA工具,我们提供一系列的脚本范例。

跟随处理器核,我们同时提供一系列基于AMBA总线的周边,包括:UART,SPI,I2C™,I2S,Timer,PWM,Watchdog,GPIO,PS/2,RTC,Ethernet MAC,USB,FIFO,Scatter-Gather DMA,AES,SHA,ECC和quad-SPI闪存接口。 得益于使用业界标准的总线协议,eSi-3200同时兼容广泛的第三方IP。

根据客户的需求,我们可以生成多层的AHB矩阵和APB总线来连接eSi-3200处理器,内存和外设。