eSi-RISC Development Suite

The eSi-RISC Development Suite contains all of the software tools needed for embedded application development for eSi-RISC processors. The Development Suite is available on Windows, Linux and macOS and is free to use for eSi-RISC processor licensees.

Download the latest release of the eSi-RISC Development Suite.

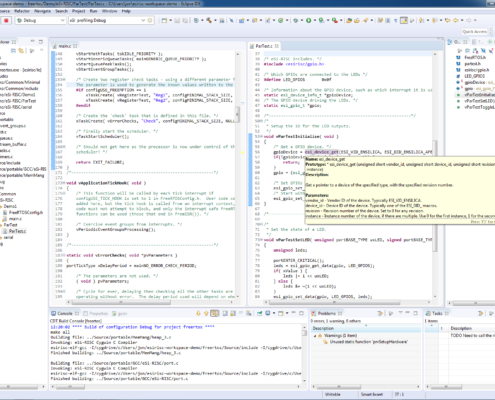

IDE

The Eclipse IDE is used by millions of software developers worldwide. It provides a fully functional C and C++ Integrated Development Environment, including:

- Project management, including toolchain option setting and makefile creation, supporting separate release and debug configurations.

- Source navigation (type hierarchy, call graphs, browser).

- Code editor with syntax highlighting, folding, auto-completion, source code refactoring, context sensitive help.

- Multi-core source-level debugger, including I/O console, memory, register and diassembler views.

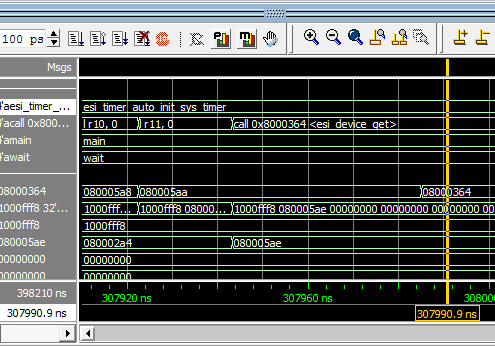

- Debug targets include eSi-RISC ASICs and FPGAs via USB/JTAG, an integrated instruction set simulator and RTL simulation via PLI.

- Integrated graphical source code version control tools (GIT, Subversion and others).

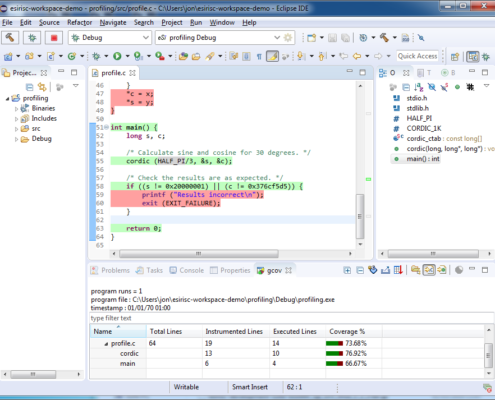

- Graphical profiling and code coverage.

- Documentation and sample applications for eSi-RISC processors, peripherals and libraries.

C/C++ Compiler

The eSi-RISC Development Suite provides GCC as its C/C++ compiler. GCC is one of the most widely used compilers, as it used by most desktop and server Linux distributions. While the compiler language front-end and middle-end optimisation engines are common, a machine-dependent backend implements support for the eSi-RISC architecture.

- Supports all major C and C++ standards (E.g. ANSI C, C99, C11, C++17).

- Can optimise for code size or performance.

- Supports whole program optimisation (Link Time Optimisation (LTO)).

- Auto-vectorization can utilise eSi-RISC’s SIMD instruction set.

- Supports eSi-RISC’s user-defined instructions via built-in functions.

- Interrupt handlers can be written in C.

- Generates debug, coverage and profiling information.

- Supports both 16-bit and 32-bit eSi-RISC processors, and understands which instructions and registers are available in a particular configuration and optimises accordingly.

- Supports hardware floating point instructions if available, with a backup of high-performance hand-written assembler software emulation, if not.

- C, C++, math and eSi-RISC libraries are compiled optimised for both size and speed for each CPU configuration, to take advantage of all available features.

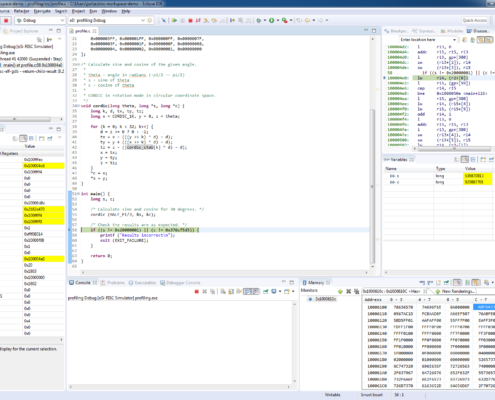

Debugger

Integrated in to the Eclipse IDE, but also available as a standalone application, is the GDB debugger. GDB provides full source level debugging for both C and C++ applications. It supports:

- Hardware ASIC & FPGA targets via USB/JTAG and serial connections. Hardware targets can also be debugged remotely over TCP/IP so do not have to be physically attached to the debug host PC.

- Debugging of Verilog RTL and gate-level simulations via a TCP/IP connection to a simulator (ModelSim/Incisive/VCS) using a PLI.

- An integrated instruction set simulator target. The instruction set simulator allows software to be developed before hardware is available. It can generate profiling and trace information and supports peripheral emulation (UART, LCD, Ethernet) as well as user-defined instructions and peripheral models.

- Multiprocessor debug.

- Debug of both RAM and ROM or Flash based code.

- Download of code to RAM and programming of SPI Flash & TSMC embedded Flash.

- Ability to attach to running target, or debug from reset.

- Software and hardware breakpoints with conditions.

- Hardware watchpoints (data breakpoints), can be set on reads, writes or either access, with optional conditions (E.g. break when a specific value is written to a given address or address range).

- Hardware single stepping.

- Disassembler and stack (backtrace) viewer.

- View registers (including floating point, vector and system CSRs) and memory, in multiple formats.

- Allows O/S system calls on the target to be redirected to the host, allowing for stdin/stdout to be directed to the Eclipse console and also for the target to read and write files on the host’s filesystem.

- Supports control of lab test equipment by s/w on the target CPU using a VISA over JTAG interface.

- Python scripting and a machine-interface (MI) to allow control by your own applications.

RTOS Support

- FreeRTOS –

Developed in partnership with the world’s leading chip companies over a 15 year period, the FreeRTOS kernel is a market leading real time operating system (or RTOS), and the de-facto standard solution for microcontrollers and small microprocessors. FreeRTOS is included in the eSi-RISC Development Suite.

Developed in partnership with the world’s leading chip companies over a 15 year period, the FreeRTOS kernel is a market leading real time operating system (or RTOS), and the de-facto standard solution for microcontrollers and small microprocessors. FreeRTOS is included in the eSi-RISC Development Suite. - uC/OS –

µC/OS is a full-featured embedded operating system. It features support for TCP/IP, USB, CAN bus, as well as Modbus and includes a robust file system and graphical user interface. μC/OS kernels allow for unlimited tasks and kernel objects. The kernels’ memory footprint can be scaled down to contain only the features required for your application, typically 6–24 KBytes of code space and 1 KByte of data space.

µC/OS is a full-featured embedded operating system. It features support for TCP/IP, USB, CAN bus, as well as Modbus and includes a robust file system and graphical user interface. μC/OS kernels allow for unlimited tasks and kernel objects. The kernels’ memory footprint can be scaled down to contain only the features required for your application, typically 6–24 KBytes of code space and 1 KByte of data space. - Thread X –

THREADX RTOS is Express Logic’s advanced Industrial Grade Real-Time Operating System (RTOS) designed specifically for deeply embedded, real-time, and IoT applications. THREADX RTOS provides advanced scheduling, communication, synchronization, timer, memory management, and interrupt management facilities. In addition, THREADX RTOS has many advanced features, including its picokernel™ architecture, preemption-threshold™ scheduling, event-chaining,™ execution profiling, performance metrics, and system event tracing.

THREADX RTOS is Express Logic’s advanced Industrial Grade Real-Time Operating System (RTOS) designed specifically for deeply embedded, real-time, and IoT applications. THREADX RTOS provides advanced scheduling, communication, synchronization, timer, memory management, and interrupt management facilities. In addition, THREADX RTOS has many advanced features, including its picokernel™ architecture, preemption-threshold™ scheduling, event-chaining,™ execution profiling, performance metrics, and system event tracing. - Phoenix-RTOS – Phoenix-RTOS is an open-source, microkernel-based, realtime operating system for resource constrained devices. Phoenix-RTOS is an ideal platform for software defined IoT communication stacks and other applications with realtime processing requirements.

- Erika Enterprise –

Erika Enterprise is a royalty free automotive OSEK/VDX certified Hard Real Time Operating System (RTOS). Main features: Hard Real-Time support with Fixed Priority Scheduling and Immediate Priority Ceiling; Support for multicore/manycore architectures; 1-4 Kb Flash footprint; Support for stack sharing among tasks; Dual License: Open-source and commercial.

Erika Enterprise is a royalty free automotive OSEK/VDX certified Hard Real Time Operating System (RTOS). Main features: Hard Real-Time support with Fixed Priority Scheduling and Immediate Priority Ceiling; Support for multicore/manycore architectures; 1-4 Kb Flash footprint; Support for stack sharing among tasks; Dual License: Open-source and commercial.